Tugas Pendahuluan 2 Modul 1

(Percobaan 2 Kondisi 6)

Percobaan 2 Kondisi 6

Buatlah rangkaian seperti pada modul percobaan, kemudian buatlah kondisi dengan inputan berupa saklar SPDT .

- Rangkaian Sederhana 1 : B= 1, D=0, A=1, C’=1, D= 1

- Rangkaian Sederhana 2 : B= 1, D=0, A= 1, B=1, C’=1.

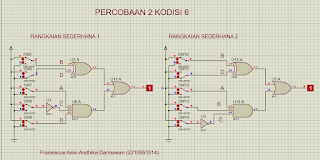

2. Gambar Rangkaian Simulasi[Kembali]

Sebelum dijalankan

Setelah dijalankan

3. Video Simulasi[Kembali]

4. Prinsip Kerja[Kembali]

a. Rangkaian sederhana 1

Pada rangkaian pertama kita memiliki 5 saklar SPDT, 1 Gerbang XOR, 1 Gerbang NOT, 1 Gerbang OR, dan 1 Gerbang AND dan Logicprobe yang diposisikan seperti pada gambar.

Saat rangkaian diberi sumber tegangan sebesar 5v maka arus akan mengalir pada swicth B yang berlogika 1 dan D yang berlogika 0, sesuai dengan konidisi yang diminta. selanjutnya pada gerbang logika xor dimana pada gerbang logika xor bersifat exlusif, di mana keluarannya akan bernilai nol jika penjumlahan dari biner inputnya bernilai genap, sedangkan jika penjumlahan binernya ganjil maka outputnya akan bernilai 1. pada rangkaian 1 di percobaan 2 switch B dan D memiliki logika 1 maka gerbang logika xor bersifat ganjil karena 1 + 0 = 1 dimana 1 adalah angka ganjil, sehingga outputnya akan berlogika satu.

Lalu pada gerbang logika AND yang menerapkan sistem perkalian artinya keluaran akan bernilai 1 jika semua nilai input adalah 1, dan jika salah satu atau lebih input ada yang bernilai nol maka output akan bernilai nol. Dari kondisi ini semua swicth pada gerbang logika AND berlogika 1 tetapi pada c' memiliki gerbang logika NOT yang outputnya berlawanan dengan inputnya (bersifat invers) sehingga outputnya berlogika 0. hal ini menyebabkan output dari gerbang logika and ini beroutput 0 karna salah satu inputnya erlogika nol. sehingga pada output dari gerbang AND akan bernilai 0 karena ada salah satu input dari 3 input yang bernilai nol.

Selanjutnya pada gerbang logika OR yang menerapkan prinsip penjumlahan, dimana jika salah satu atau lebih input bernilai 1 maka output akan bernilai 1 . Nilai output bernilai 0 hanya pada jika nilai semua input bernilai 0. pada kondisi pada percobaan ini salah satu input dari gerbang logika or bernilai satu maka output dari gerbang or akan bernilai satu sehingga logicprobe menunjukkan biner 1.

b. Rangkaian Sederhana 2

Pada rangkaian ke-2 kita memiliki 5 saklar SPDT, 1 Gerbang XOR, 1 Gerbang NOT, 1 Gerbang OR, dan 1 Gerbang AND dan Logicprobe yang diposisikan seperti pada gambar.

Saat rangkaian diberi sumber tegangan sebesar 5v maka arus akan mengalir pada swicth B yang berlogika 1 dan D yang berlogika 0, sesuai dengan konidisi yang diminta. selanjutnya pada gerbang logika xor dimana pada gerbang logika xor bersifat exlusif, di mana keluarannya akan bernilai nol jika penjumlahan dari biner inputnya bernilai genap, sedangkan jika penjumlahan binernya ganjil maka outputnya akan bernilai 1. pada rangkaian 1 di percobaan 2 switch B dan D memiliki logika 1 maka gerbang logika xor bersifat ganjil karena 1 + 0 = 1 dimana 1 adalah angka ganjil, sehingga outputnya akan berlogika satu.

Lalu pada gerbang logika AND yang menerapkan sistem perkalian artinya keluaran akan bernilai 1 jika semua nilai input adalah 1, dan jika salah satu atau lebih input ada yang bernilai nol maka output akan bernilai nol. Dari kondisi ini semua swicth pada gerbang logika AND berlogika 1 tetapi pada c' memiliki gerbang logika NOT yang outputnya berlawanan dengan inputnya (bersifat invers) sehingga outputnya berlogika 0. hal ini menyebabkan output dari gerbang logika and ini beroutput 0 karna salah satu inputnya erlogika nol. sehingga pada output dari gerbang AND akan bernilai 0 karena ada salah satu input dari 3 input yang bernilai nol.

Selanjutnya pada gerbang logika OR yang menerapkan prinsip penjumlahan, dimana jika salah satu atau lebih input bernilai 1 maka output akan bernilai 1 . Nilai output bernilai 0 hanya pada jika nilai semua input bernilai 0. pada kondisi pada percobaan ini salah satu input dari gerbang logika or bernilai satu maka output dari gerbang or akan bernilai satu sehingga logicprobe menunjukkan biner 1.

5. Download[Kembali]

Link Datasheet Gerbang Logika klik disini

Tidak ada komentar:

Posting Komentar